- JTAG

-

JTAG, un acrónimo para Joint Test Action Group, es el nombre común utilizado para la norma IEEE 1149.1 titulada Standard Test Access Port and Boundary-Scan Architecture para test access ports utilizada para testear PCBs utilizando escaneo de límites.

JTAG se estandarizó en 1990 como la norma IEEE 1149.1-1990. En 1994 se agregó un suplemento que contiene una descripción del boundary scan description language (BSDL). Desde entonces, esta norma fue adoptada por las compañías electrónicas de todo el mundo. Actualmente, Boundary-scan y JTAG son sinónimos.

Diseñado originalmente para circuitos impresos, actualmente es utilizado para la prueba de submódulos de circuitos integrados, y es muy útil también como mecanismo para depuración de aplicaciones empotradas, puesto que provee una puerta trasera hacia dentro del sistema. Cuando se utiliza como herramienta de depuración, un emulador en circuito que usa JTAG como mecanismo de transporte permite al programador acceder al módulo de depuración que se encuentra integrado dentro de la CPU. El módulo de depuración permite al programador corregir sus errores de código y lógica de sus sistemas.

Contenido

Características Eléctricas

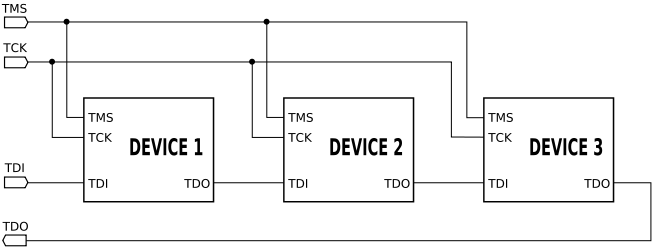

Una interfaz JTAG es una interfaz especial de cuatro o cinco pines agregadas a un chip, diseñada de tal manera que varios chips en una tarjeta puedan tener sus líneas JTAG conectadas en daisy chain, de manera tal que una sonda de testeo JTAG necesita conectarse a un solo "puerto JTAG" para acceder a todos los chips en un circuito impreso. Los pines del conector son

- TDI (Entrada de Datos de Testeo)

- TDO (Salida de Datos de Testeo)

- TCK (Reloj de Testeo)

- TMS (Selector de Modo de Testeo)

- TRST (Reset de Testeo) es opcional.

Ya que posee una sola línea de datos, el protocolo es necesariamente serial, como el Serial Peripheral Interface. La entrada de la señal de reloj es por el pin TCK. La configuración del dispositivo se realiza manipulando una máquina de estados de un bit empleando el pin TMS. Un bit de datos es cargado en TDI y otro sacado en TDO por cada pulso de reloj de la señal TCK. Se pueden cargar diferentes modo de instrucción como leer el ID del chip, muestrear el valor de pines de entrada/salida, manejar pines de salida, manipular funciones del chip, o funciones de bypass que unen el pin TDI con TDO para lógicamente unir cadenas de varios chips (chips en cascada). La frecuencia de trabajo de la señal de reloj del pin TCK varía en función de cada chip, pero típicamente está en el rango de 10-100 MHz (10-100ns/bit).

Cuando se hace la operación de boundary scan en circuitos integrados, las señales manipuladas están entre diferentes bloques funcionales del chip, más que entre diferentes chips.

El pin TRST es una señal opcional bajo-activa para reseteo o reinicio de la prueba lógica (por lo general asíncrona, pero que a veces está sincronizada con el reloj, dependiendo del chip). Si no se dispone de dicho pin, la prueba lógica puede reiniciarse mediante una instrucción reset.

Existen productos de consumo que tienen un puerto JTAG integrado, por lo que las conexiones están a menudo disponibles en la PCB como parte de la fase de prototipado del producto. Estas conexiones pueden proporcionar una sencilla forma de realizar ingeniería inversa.

Extensiones Comunes

Extensiones de fabricantes: Infineon, MIPS EJTAG, Freescale COP, ARM ETM (Extended Trace Macrocell), OnCE etc.

Aplicaciones

- Casi cualquier sistema embebido tiene un puerto JTAG.

- El conector del bus PCI posee pines JTAG.

- Existe una tarjeta especial JTAG que se puede usar para regrabar una BIOS dañada.

Software Cliente

La interfaz JTAG es accesible por medio de aplicaciones de JTAG.

Software Libre

- Very cheap interface working with the CICLaMaB program

- OpenCores JTAG module is an IP core which can be used to provide JTAG in a design. It is part of the OpenCores project

- The openwince project produce the JTAG Tools supporting a large set of inexpensive IEEE 1284 parallel printer port cables (the project has made no releases since 2003 but its CVS repository is quite active)

- JTAG-ARM9 provides a JTAG access program for the ARM9 processor.

- JTAG for the LART aimed at the LART processor

- JTAG base layer is an attempt at creating a JTAG library

- The uCLinux for Blackfin project have a JTAG-backend for the GNU Debugger and a JTAG Tools version specifically for Blackfin based on the openwince work

- JTAG toolkit is a free software JTAG tool suite, including API library and several examples

- OpenOCD is an GPL Open Source GDB Server that currently supports ARM7 and some ARM9 Targets

- Boundary Scan Coach An interactive learning software for IEEE Std.1149.x

- Open JTAG

- UrJTAG aims to create an enhanced, modern tool for communicating over JTAG with flash chips, CPUs, and many more

Software propietario

- JTAG Technologies Test and programming development systems.

- TopJTAG Circuit visualization and debugging software employing boundary-scan (IEEE 1149.1 JTAG) technology.

- JTAG ScanWorks JTAG development systems.

- Green Hills Software MULTI Debugger and Green Hills Probe, Software and hardware supports JTAG and BDM based development on ARM, XScale, PowerPC, MIPS, ColdFire, Blackfin, ARC, TI C6000, v800, StarCore, SH, M32R, and LSI ZSP.

- Ronetix PEEDI, JTAG Emulator and Flash Programmer for ARM7/9, XScale

- SEGGER Microcontroller Systeme GmbH j-link, USB to JTAG interface for ARM cores (J-Flash, J-Mem, RDI Pro Bundle)

- Lauterbach Datentechnik GmbH produce JTAG-based in-circuit emulators the most popular being TRACE 32

- Macraigor Systems LLC JTAG Commander and OCD Commander

- Abatron AG's BDI-2000 acts as a GDB server on your LAN, giving you source-level debugging via JTAG.

- JTAG Emulator Embedded Toolsmiths Guardian-SE JTAG Emulator connects a GDB server on your LAN to the JTAG interface on PowerPC, MIPS, XScale and Arm Processors. This allows: JTAG FLASH Programming, JTAG Emulation and JTAG source-level debugging via JTAG for PowerPC, MIPS, XScale and ARM Processors.

- XJTAG Development System

- Göpel electronic SCANFLEX, JTAG / Boundary Scan test and In-System Programming, debug, emulation

- Corelis ScanExpress

- GOEPEL Electronics JTAG / Boundary Scan test and In-System Programming, debug, emulation at device, board, and system level; SYSTEM CASCON, SCANFLEX, CASLAN.

- Wind River MultiCore Debugger, Wind River OCD, Probe, ICE and Trace tools JTAG support along with HW reference development boards.

Enlaces externos

- JTAG en hardware-hacking.com . Link roto

- JTAG/Boundary-scan explained Knowledge base plus industry links

- JTAG FAQ

- A Brief Introduction to the JTAG Boundary Scan Interface

- Overview of JTAG technology

- JTAG Scan Educator - Ver. 2 (Rev. A) - An educational software program for DOS, JTAG Scan Educator, introduces the fundamentals of the IEEE 1149.1 boundary-scan standard, including architecture protocol, and required instruction sets.

- Boundary Scan Testing A great tutorial with more in depth detail about operations

- Boundary Scan Coach An interactive learning software for IEEE Std.1149.x

- K9JTAG - A cheap do it yourself parallel port JTAG debugger for ARM microcontrollers.

- JTAG Programmer

Categorías:- Protocolos

- Lenguajes de especificación

- Siglas de informática

Wikimedia foundation. 2010.